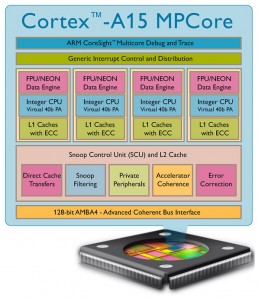

ARM has just unveiled a new ARM Cortex-A15 MPCore quad-core chip, clocked at up to 2.0GHz, built using the TSMC 28-nanometer HPM process. It includes ARM’s NEON and Floating Point Unit technology, EEC for L1 and L2 RAM, as well as the ability to address more than 4GB of RAM.

Even if the new chip brings more processing power, it is very energy efficient as well, offering similar power consumption ratings to existing Cortex-A9 products. As if that was not enough, it also supports virtualization which makes it suitable for a wide variety of applications.

The Cortex-A15 MP4 Hard Macro is a high performance, power-optimized quad-core hard macro implementation of their flagship Cortex-A15 processor, on leading 28nm process. It delivers three significant firsts for the ARM hard macro portfolio. Not only is it the first quad–core hard macro, but also the first hard macro based on the highest performance ARMv7 architecture-based Cortex-A15 processor, and it is also the first hard macro based on 28nm process.

In terms of configuration, the Cortex-A15 MP4 Hard Macro includes:

- NEON™ and Floating Point Unit (FPU) technology

- ECC for L1 and L2 RAMs (L1-I cache has single bit parity)

- 2x32KB L1 and 2MB L2 caches

- 224 interrupts, 6 power domains

- AMBA Domain Bridge, CoreSight™, APB, ATB, Funnel

The hard macro has been developed using ARM Artisan® 12-track libraries and Processor Optimization Pack™ (POP) solutions for the Cortex-A15 processor on TSMC 28nm HPM process.

According to Haydn Povey, Director of Marketing in the ARM Processor Division, one of the biggest challenges in designing high-performance systems on the latest nodes is keeping the power profile and leakage levels really low. The new Cortex-A15 hard macro manages to delivering performance of more than 2GHz, and in excess of 20,000DMIPS. At the same time it manages to maintain the power efficiency of the Cortex-A9 hard macro. “This makes this latest macro offering from ARM a real and timely boon to SoC designers venturing into what are for many, unchartered territories”, writes Haydn Povey on AMD’s official blog.